本文转自公众号,欢迎关注

PSRAM完全解读 (qq.com)

PS RAM完全解读

一. PSRAM概述

PSRAM即伪静态RAM,要讲到PSRAM首先得从SRAM和 DRAM讲起。

SRAM和DRAM都代表易失性的存储形式,当 电源掉电时内容丢失。SRAM使用六 晶体管存储单元存储数据,速度更快,效率更高(比dram需要更少的功率),允许数据残留,并且通常更昂贵, 接口简单, 驱动简单。

相比之下,DRAM通过结合金属氧化物 半导体场效应晶体管( MOSFET)和金属氧化物半导体(MOS) 电容器来实现数据存储,DRAM 芯片更便宜,但需要从外部源不断刷新以保留其 电容器上的数据,接口复杂,驱动复杂。

那么有没有一种RAM能结合SRAM和DRAM的优点,即容量大,又接口驱动简单呢,有,因为有以上需求于是PSRAM应运而生,PSRAM接口和SRAM一样简单,驱动简单;而存储形式则和DRAM一样,容量远大于SRAM,介于SRAM和DRAM之间,现在一般是最大64MB。

美光科技联合华邦 电子 (Winbond Electron ics)、Gig aDevice Semiconduct or 和 AP Memory Technology 创立了Xccela 联盟, 其中 Xccela Bus 接口即PSRAM使用的接口。

二. PSRAM厂家

PSRAM厂家也有很多,以AP用的最多。

华邦

64Mb

W956D6KBK 1.8V/1.8V 133MHz -40℃~85℃ 4Mb x16 CRAM-ADM - P

256Mb

W968D6DAG 1.8V/1.8V 133MHz -40℃~85℃ 16Mb x16 CRAM - P

W968D6DAG 1.8V/1.8V 133MHz -40℃~85℃ 16Mb x16 CRAM - P

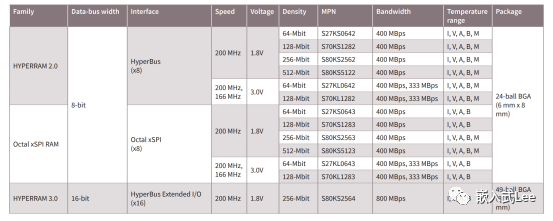

英飞凌

有多种接口,容量可选最大64MB

Apmemory

PSRAM的老大哥,最大到64MB

三.PSRAM详解

以APS256XXN-OBRx DDR Octal SPI PSRAM 为例进行详解。

2.1特征

电源

单电源 供电,VDD和VDDQ内部连接,电源范围1.62到 1.98V。

接口

Octal SPI接口支持DDR,即双边沿传输。

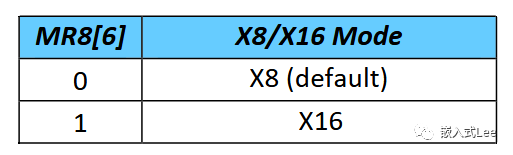

支持x8模式(默认)和x16模式,可以通过配置 寄存器选择

X8模式,一个CLK传输2个字节数据,x16模式一个CLK传输4个字节数据,因为是双边沿传输。

默认x8模式,可以通过寄存器MR8[6]=1改为x16模式。

性能

时钟最大200MHz,所以最大速度是x8模式400MB/s,x16模式800MB/s。

组织

256Mb X8 模式

一个PAGE大小2048字节 总容量32M x 8bits即32MB

行地址AX[13:0],列地址AY[10:0]

256Mb X16 模式

一个PAGE大小2048字节 总容量16M x 16bits即32MB

行地址AX[13:0],列地址AY[9:0] 一个列地址对应16bits即2字节,所以地址范围是[9:0].

不管什么模式页总是2KB,x16模式页地址只需要CA[9:0]因为单位是2B了。

刷新

自刷新,无需发送命令。

操作温度范围

TOPER = -40°C to +85°C 标准范围

TOPER = -40°C to +105°C 扩展范围

典型待机电流

Halfsleep模式,数据保持,@ 25°C时40µA

最大待机电流

1100µA @ 105°C

680µA @ 85°C

可以看到温度对待机电流影响较大。

低功耗特征

分区自刷新PASR,

自动温度补偿自刷新(AT CSR),内部自带 温度传感器,根据温度控制刷新率,温度越高刷新率越高

软件复位

支持软件命令方式实现上电复位效果

引脚复位

不是所有封装都有

输出驱动能力

LVCMOS输出,驱动能力可以通过寄存器配置

DM/DQS

写操作支持DM

读操作支持DQS,DM,DQS共用引脚。

读写延迟

可通过寄存器配置读写延迟时间

写Bu rst长度

最大X8模式2048 x8bits ,X16模式1024x16bits

最小X8模式2x8bits ,X16模式2x16bits

即最大一个PAGE的大小,最小时一个总线宽度的呃倍,因为是DDR双边沿传输。

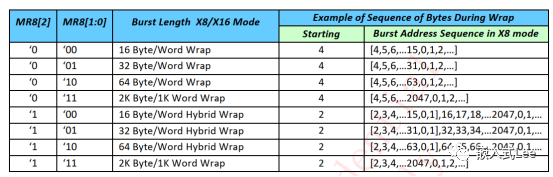

Wrap & hybrid burst

X8模式16/32/64/128/2K 单位Bytes

X16模式16/32/64/128/1K 单位Words(2B)

线性Burst命令

该命令即Burst固定为最大2KB

列地址自动递增

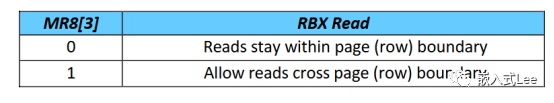

可以通过寄存器配置使能RBX

即读操作时到了页边界,页地址自动递增,而不需要重新发送页地址。

2.2 引脚 信号

重点需要理解DQS/DM0和DQS/DM1这两个引脚信号。

DQS和DM复用

DM由主机驱动,表示写时数据是否MASK掉的,为1表示MASK掉即不需要写

DQS由设备驱动,表示数据是否有效的,DQS=1表示数据有效。

可以这样理解,DQS和DM都是谁发数据由谁驱动,告诉接收方对应的字节数据是否有效。

DQS是和DQ数据同时更新的。

| 引脚 | 类型 | 描述 | 说明 |

|---|---|---|---|

| VDD | 电源 | Core 和IO 电源1.8V | VDDQ 内部连接到VDD |

| VSS | 地 | Core和IO 电源地 | |

| A/DQ[7:0] | IO | 地址/数据总线[7:0]注意发送地址始终是用的[7:0],不会用高16位。 | X8 和X16模式使用 |

| DQ[15:8] | IO | 数据总线[15:8] | 只X16 模式使用 |

| DQS/DM<0> | IO | 读数据时DQ[7:0]的DQS信号,设备端驱动,为1表示数据有效。写数据时DQ[7:0]的DM信号,主机端驱动,高有效,DM=1表示MASK掉DQ[7:0]即不写。 | X8 和X16模式使用DQS和DM共用一个引脚 |

| DQS/DM<1> | IO | 读数据时DQ[15:8]的DQS信号,设备端驱动,为1表示数据有效。写数据时DQ[15:8]的DM信号,主机端驱动,高有效,DM=1表示MASK掉DQ[15:8]即不写。 | 只X16 模式使用DQS和DM共用一个引脚 |

| CE# | I | 芯片选择,低有效. CE#=1,芯片进入standby 状态. CE拉低是一次传输的开始。 | |

| CLK | I | 输入时钟 | |

| RESET# | Input | 复位信号,低有效. 可选的内部连接固定电平。 | 不是所有封装都有 |

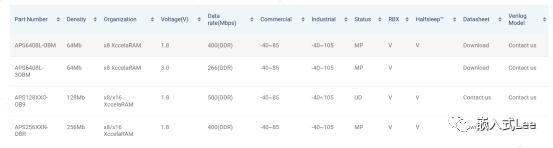

2.3 框图

可以看到VDD会进入到内部的电源调节器,可以进行电源状态控制,比如PDP和Halfsleep的管理。

PSRAM控制逻辑和IO控制部分会产生行地址,进行列地址计数,分别进行行列地址解码,输入到存储阵列,选择对一个存储单元,通过Data I/O进行数据的写入和读出。

命令地址,模式寄存器,输入到控制逻辑序列,决定上面PSRAM控制逻辑和IO控制部分的逻辑。命令和地址,寄存器的读写不经过Data I/O。

重点是时钟的控制,CLK_int进入时钟缓冲和产生模块,输出CLK_IO给Data I/O用,输出CLK_ctrl给控制逻辑用。

外部接口通过输入输出缓存和内部交互,分别到Data I/O或者到控制逻辑部分,或者到CLK_int

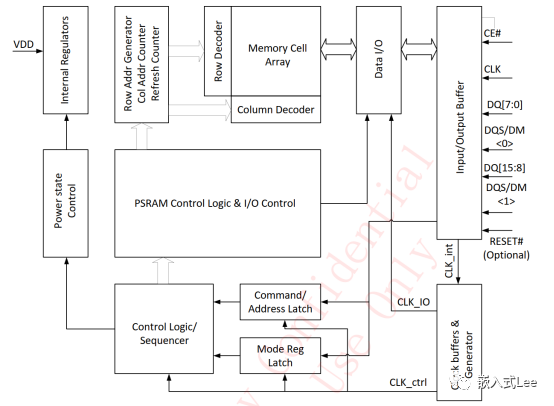

2.4 上电复位初始化时序

上电复位有两种方式,一种是通过RESET#引脚复位(有些封装该引脚未引出),直接电源的上电也是这种方式;还有一种是发送Global Reset命令。两种方式复位的效果一致。

上电复位的效果是所有寄存器恢复到默认状态,RAM中的内容不保证状态。

有几个时间点需要注意

1.复位完成后即可进入 SDR模式,既可以进行单速率读。

然后即可进行正常的所有操作(如果是VDD刚上电则需要满足后面相应的条件才能进行PDP和Halfsleep操作)。

2.VDD达到VDDmin至少要≥500uS才能进行所有正常操作,除了Halfsleep之外。

3.VDD达到VDDmin至少要≥1mS才能进行所有正常操作。

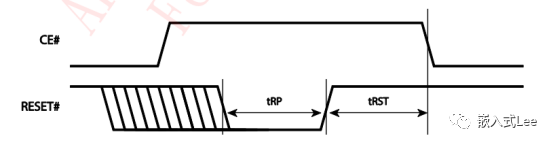

2.4.1 RESET#引脚复位

VDD/VDDQ必须达到VDDmin稳定之后,才进入初始化流程。

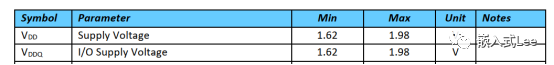

VDDmin可以从 电气 参数中查看是1.62V.

VDD稳定后进入初始化的阶段1,该阶段必须保持CE#为高,且VDD保持稳定,该阶段至少要保持tPU≥150uS。

阶段1之后的任意时候,在CE#为高时,都可以进行RESET#的拉低来进行复位,拉低时间需要tRP≥1uS

然后释放RESET#,释放时间要≥2uS。所有RESET#引脚复位至少需要3uS,复位过程对应阶段2。

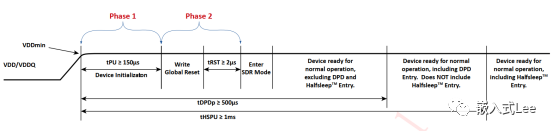

2.4.2 Global Reset命令复位方式

在阶段1之后,任意时间,可以发送0xFF指令进行上电复位,即上图的阶段2部分。

CE#拉低tCSP之后CLK的第一个边沿和第二个边沿发送INST,即A/DQ[7:0]=0xFF,此时DQS/DM

不关心。注意A/DQ[7:0]的建立时间至少要tSP,即CLK上升沿tSP之前数据就要准备好,数据保持时间需要tHD以上,即CLK下降沿之后数据至少还要保持该时间。发完INST之后,CLK再发送3个CLK,最后一个CLk的下降沿tCHP之后CE#开始拉高释放,此时开始真正的复位。

CE#释放拉高之后的tCSP2时间后,CLK不再关心可有可无。tRST时间后复位完成。

即必需tRST时间之后,CE#才能再次拉低,进行后续操作。

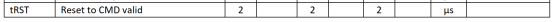

相关时序参数值如下:

2.5 接口描述

2.5.1 地址空间

读写数据,地址必须是偶数对齐,即地址的A[0]必须为0, 所以x8模式是2B对齐,x16模式是4B对齐。读写寄存器无该要求,可以指定任意对应可读写的寄存器。

2.5.2 Burst类型和长度

读写默认是Hybrid Wrap 32 模式,可通过寄存器配置为x8模式的16B,32B,64B,2KB,x16模式的16words,32words,64words,1Kwords。

专有的命令还支持 Linear Burs ting模式。

Bursts长度写最少要是x8模式2B,x16模式4B,读无最小限制。

读写的最大Burst长度不受限制,但是一次传输不能超过tCEM的时间。

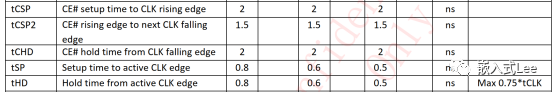

2.5.3 命令地址发送

CE#拉低之后,指令在第一个CLK的上升沿和下降沿被设备锁存。从第二个CLK开始的2个CLK共4个边沿发送4个字节的地址,都是边沿设备锁存数据。

所以3个CLK共6个边沿发送命令+地址。命令实际只有一个字节,在上下沿保持不变发送的是同样的内容,地址4个字节。

2.5.4 命令表

指令和地址总是只使用A/DQ[7:0]不管是x8还是x16模式。

x16模式 列地址不需要CA10,CA[9:0]足够,因为单位是2字节了。

Linear Burst 命令0x20,0xA0,Burst固定,不受MR8[2:0]的配置影响

只有Linear Burst读支持RBX,即自动页地址递增。

如下图

其中x表示关心可以任意值

A3 = 7'bx, RA[13] {未使用位保留}

A2 = RA[12:5]

A1 = RA[4:0],CA[10:8] { CA[10] 只在 X8 模式有}

A0 = CA[7:0] 注意CA[0]始终是0

MA = 模式寄存器地址

其中Sync Read和Sync WriteBurst的Burst由MR[8:0]配置

Linear Burst Read和Linear Burst Write固定为Linear Burst即页大小,不受MR[8:0]影响,该模式支持RBX(需要寄存器配置使能)。

Mode Register Read和Mode Register Write支持从任意寄存器开始读写(和寄存器的读写属性要对应)。

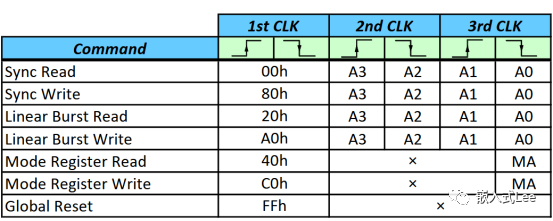

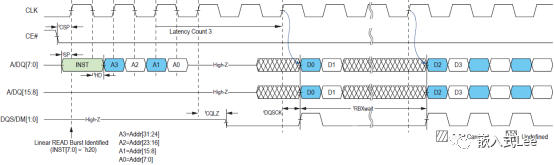

2.5.5 读操作

CE#拉低后的开始3个CLK发送完命令和地址, 设备从第三个CLK的上升沿即发送A1时开始拉低DQS/DM。

延迟LC时间后,A/DQ[7:0]输出数据,由于内部刷新机制,延迟时间可能是LC~LCx2之间。

第一个DQS/DM的上升沿表示设备输出的数据有效。

不管是x8模式还是x16模式,命令和地址都只使用A/DQ[7:0],如果是x16模式则返回数据时A/DQ[7:0]输出和A/DQ[7:0]完全一样。

同步读模式

( Synchronous Read )

1.CE#拉低表示一次传输开始,tCSP之后CLK开始拉高发送命令INST

2.在CLK的上升沿之前tSP数据就要准备好,即数据的建立时间

3.CLK下降沿之后tHD之后,数据还需要保持,即数据的保持时间

4.第4个CLK上升沿之后tCQLZ开始拉低,表示PSRAM收到指令了正在准备数据,此时主机还不能去读数据,数据还未就绪。

5.A1对应的上升沿之后的LC时间(默认是5个CLK),之后设备才会输出数据,这里是读延迟时间。

6.LC之后的第一个上升沿之后的tDQCLK时间后,DQS/DM才会拉高,表示PSRAM输出数据有效 DQS/DM是和DQ数据同步更新的。

7.主机在LC延迟之后,等待DQS的上升沿,捕获到DQS的上升沿后需要延时一段时间才能采样,因为DQS的上升沿DQ也才同步更新,需要一个建立时间之后才能采样数据,后面会讲这个参数。

8.CLK的下降沿tCHD之后,CE#才能拉高。

9.CE#拉高之后tHZ时间后,数据线变为高阻态。

10.CE#拉高必须至少tCPH时间.

11.一次传输至少需要tRC时间

12.一次传输CE#拉低的时间最长tCEM

线性Burst读使能RBX

( Linear Burst Read with RBX (Starting address 0xFE in X8 mode and 0x3FE in X16 mode)

和Synchronous Read一样,如果使能RBX,即(MR8[3]为1则在列地址跨页边界时,会由tRBXW ait的时间延迟,然后页地址自动递增继续读。

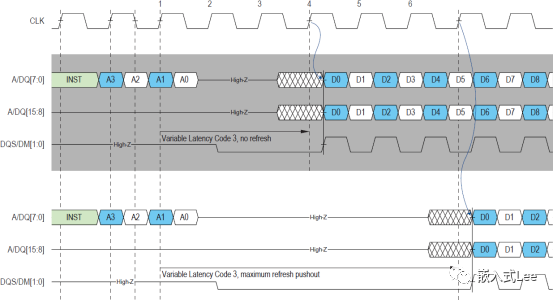

自刷新导致的读延迟增加

( **Variable Read Latency Refresh Pushout ** )

上图上面部分没有自刷新,延迟时间是3个CLK,下面部分有自刷新,所以延迟时间最大可达2x3=6CLK。

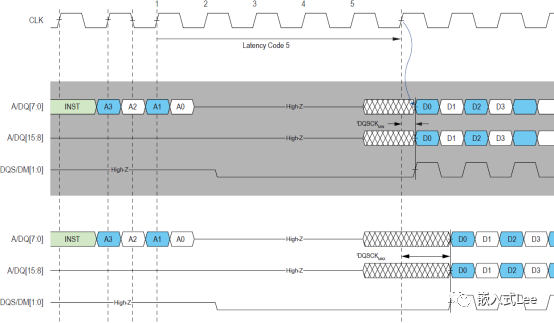

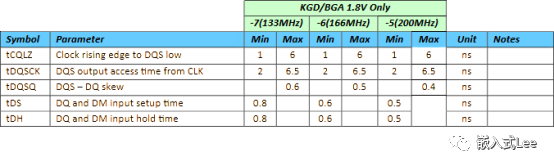

读延迟和tDQSCK

( **Read Latency & tDQSCK ** )

以上可以看到tDQSCKmin和tDQSCKMmax差异可能导致,DQS/DM第一个数据出来的时间差半个CLK,即CLK下降沿锁存数据变为上升沿锁存数据。

tDQSCK最小2nS,最大6.5nS。

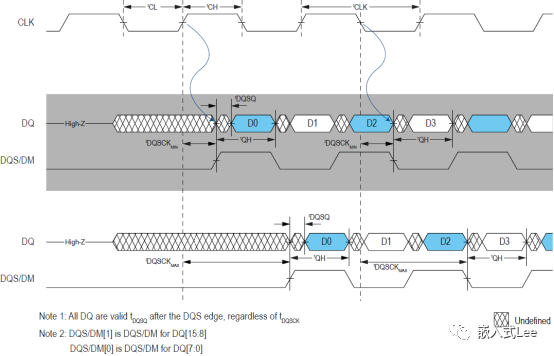

**读时DQS/DM 和 DQ **时序

( Read DQS/DM & DQ timing )

1.DQS和DQ是同步更新的。

2.DQS上升沿之后的tDQSQ时间之后,数据才有效,因为需要数据建立时间。所以读数据需要在DQS上升沿之后至少等待tDQSQ才能采样。

3.读数据是以DQS边沿为准而不是以CLK边沿为准了。

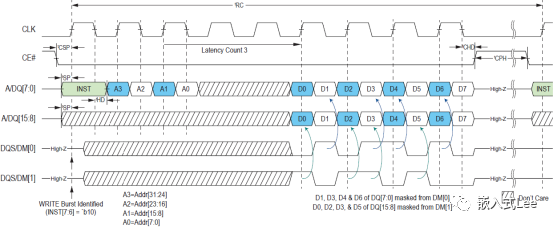

2.5.6 写操作

同步写操作

( Synchronous Write followed by any Operation )

1.tCSP,tSP,tHD,tCHD,tCPH,tRC等含义和读一样.

2.写操作x8模式最少需要写2字节,x16模式至少需要写4字节。

3.单字节的写可以通过DQS/DM的MASK来实现,DM=1表示对应字节不写。

4.指令地址总是只使用DQ[7:0], x16模式数据阶段才会使用DQ[15:8].

5.数据阶段DQ[15:8]和DQ[7:0]分别用DM[1]和DM[0]确认是否MASK掉,为1则MASK掉不写对应对应的字节。

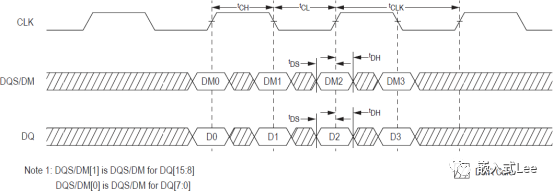

写时DQS/DM & DQ的时序

( **Write DQS/DM & DQ Timing ** )

1.CLK上升沿和下降沿建立时间tDS之前准备数据,数据保持时间tDH。即在CLK边沿前的tDS数据就要准备好,tDS后数据才能释放。

3.DM和DQ同步变化。

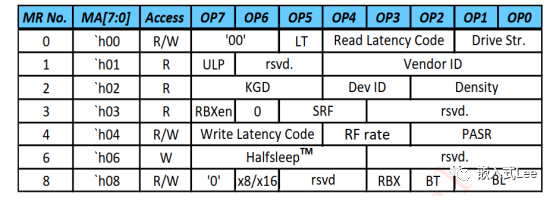

2.5.7 控制寄存器

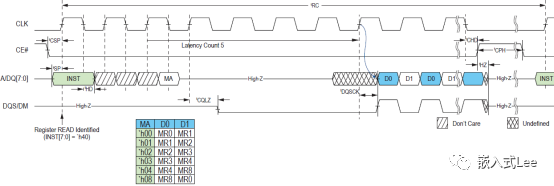

寄存器读

寄存器读写始终只使用A/DQ[7:0]

( Register Read )

1.tCSP,tSP,tHD,tRC,tCQLZ,tDQSCK,tCHD,tHZ,tCPH等参数和读数据时含义一样。

2.寄存器6只写,所以上述表格没有MA6

3.读寄存器可指定任意可读寄存器开始, 连续读则D0,D1即开始寄存器和后一个寄存器重复返回,PSRAM驱动DQS会指定只有D0有效,所以主机会重复读到D0,丢弃D1.

4.寄存器读的延迟和读数据的延迟一样,MR0[4:2]决定。

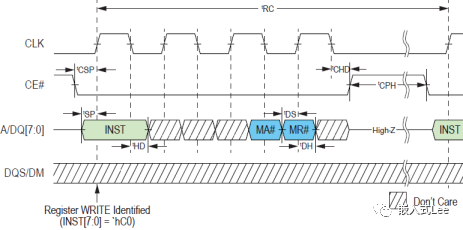

寄存器写

( **Register Write ** )

注意寄存器写没有延迟,即MA之后CLK的下一个边沿即发送MR,也不需要DM。

寄存器内容

寄存器如下,MA6只写,MA1,2,3只读,其他的可读写。

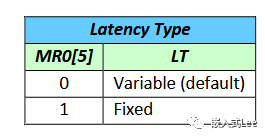

MR0[5] 读延迟类型

延迟类型1表示固定的,0表示可变的。

这里的可变是因为有刷新所以加上刷新时间可能是LC~2xLC之间任意值,

固定就是干脆就直接固定为最大值2xLC,固定的话有时候可以,方便控制器端程序。

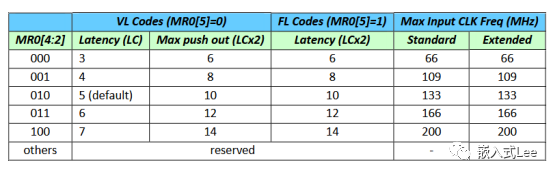

MR0[5:2] 读延迟时间设置

延迟时间设置,不同的频率需要设置不同的延迟时间,频率大延迟时间大。

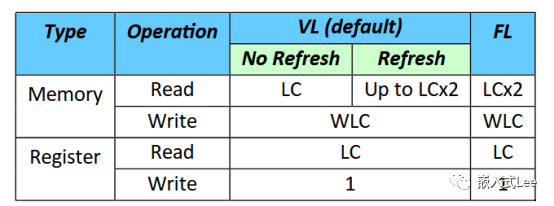

各种操作的延时

写寄存器无延迟或者说延迟是1

读寄存器是LC

写数据延时为WLC

读数据根据FL的设定可能是LC~2LC之间可变或者固定为2LC。

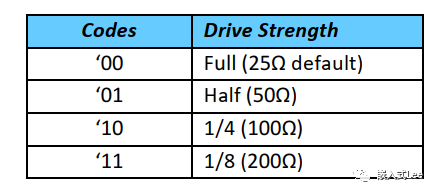

MR0[1:0] 驱动能力

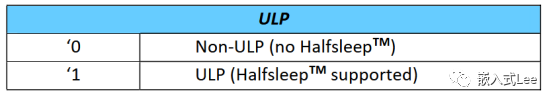

MR1[7] 支持Halfsleep能力

只读,表示是否支持超低功耗

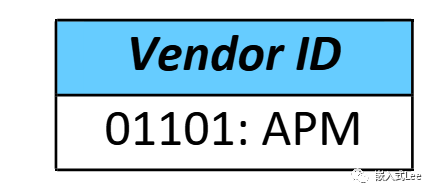

MR1[4:0] 厂商ID

只读,厂商ID

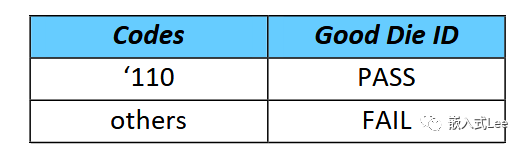

MR2[7:5] 测试状态

只读,表示是否测试OK,默认的Die没有测试时是FAIL状态,测试OK之后设置为PASS

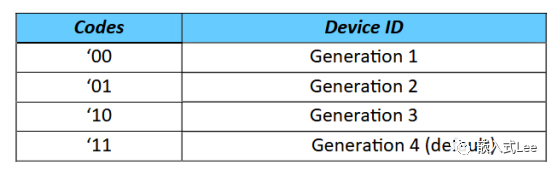

MR2[4:3] 设备ID

只读,设备ID,确认是第几代 产品

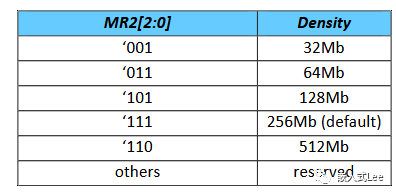

MR2[2:0] 容量

只读,确认容量大小

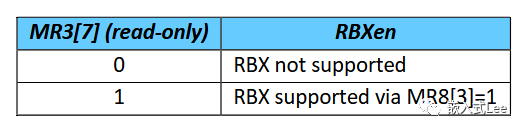

**MR3[7] **RBX模式能力

只读,确认是否支持地址自动跨页,如果支持则通过MR8[3]使能

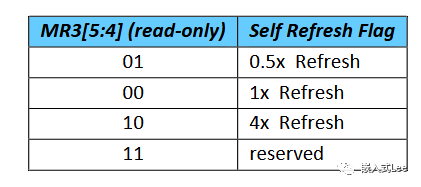

MR3[5:4] 自刷新标志

只读,当前刷新率,由MR4[4:3]和温度决定

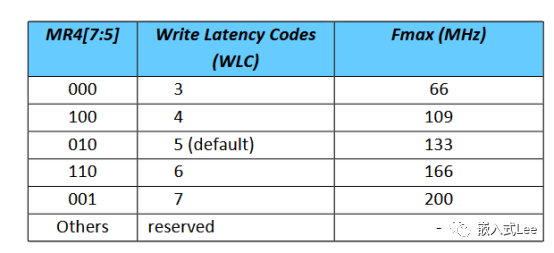

MR4[7:5] 写延迟设置

写延迟时间设置

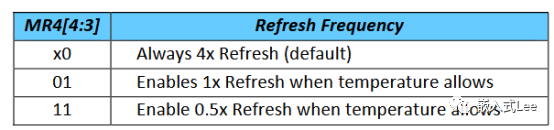

MR4[4:3] 刷新频率设置

刷新频率设置

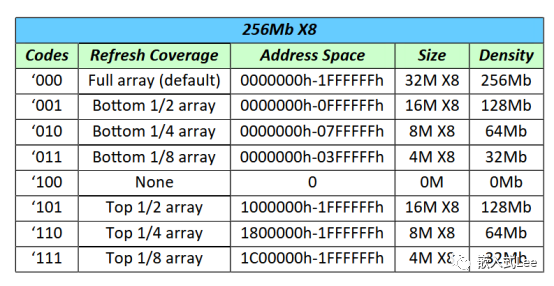

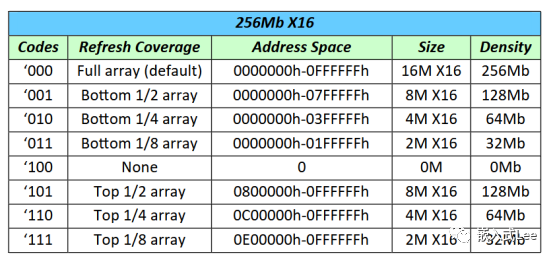

MR4[2:0] 分区刷新

16位模式只需要10位CA[9:0]既可以表示2K,1024x2B,所以不需要CA10

分区刷新可以减少待机功耗。

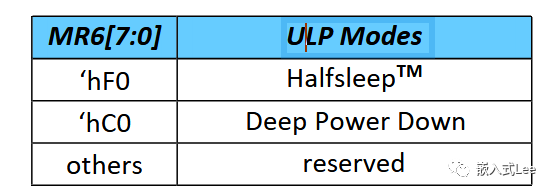

** MR6[7:0]**** Halfsleep设置**

MR8 [6] ** x8/x16模式选择**

MR8[2] Burst类型 MR8[1:0] Burst长度

线性Burst命令自动页大下Wrap,同步读命令则根据MR8[1:0]设定 Wrap

不支持RBX,即不支持自动地址递增的,一次只能最多读一页,超过绕回。

**MR8[3] **RBX读使能

需要支持RBX的才能配置,MR3[7]可以确认是不是支持RBX

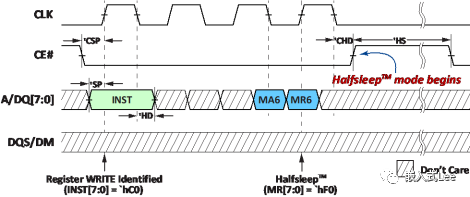

2.5.8 Halfsleep模式

(Halfsleep **Entry Write (latency same as Register Writes, WL1) ** )

Halfsleep模式下数据保持,

写寄存器MR6为0xF0进入低功耗,写完释放CE后tHS时间后才真正进入低功耗

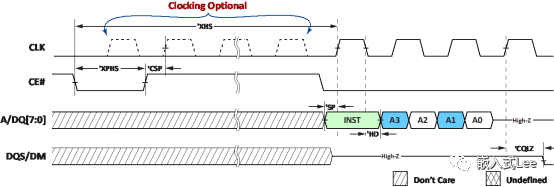

(Halfsleep **Exit (Read Operation shown as example) ** )

CE拉低触发退出低功耗,但是必须满足拉低时间超过tXPHS再释放,释放时间超过tCSP,tXHS为CE拉低后退出低功耗需要的时间,此时CLK可有可无。

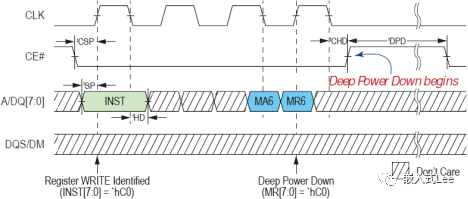

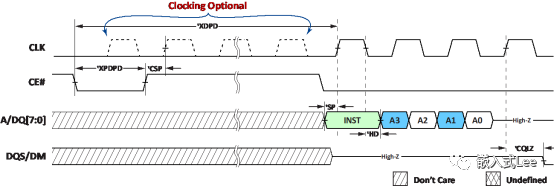

2.5.9 DPD模式 深度休眠模式

深度休眠进入和退出和Halfsleep类似,命令不同,还有就是寄存器内容和存储内容不保存,需要重新初始化。

( **Deep Power Down Entry ** )

( Deep Power Down Exit (Read Operation shown as example) )

2.6 典型参数

主要关注时序参数,其他参数可以参考手册

需要注意的是Halfsleep平均 电流很小小于100uA,但是峰值电流可达25mA,持续几十毫秒。

所以最好防止4.7uF到10uF的储能电容到VDD和VSS之间。

直流特性参数

主要注意高电平要大于0.8VDDQ

低电平要小于0.2VDDQ

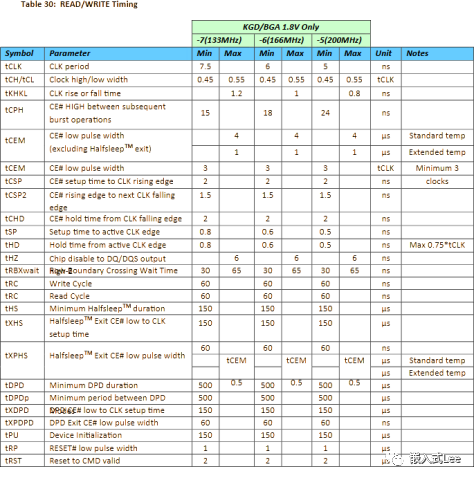

时序参数

需要注意满足各个参数的最小值

四. 总结

PSRAM有类似SRAM简单的接口,软件驱动简单,而又有DRAM高容量高性价比,所以在 IOT领域应用广泛。很多SOC, MCU,MPU都内部封装了PSRAM,用户低成本即可使用大的RAM存储。

PSRAM的时序比较简单,主要根据各个时序图理解每个时序阶段,及其参数。重点要理解DQS/DM是谁驱动的,代表什么意思, 数据采样的时间即DQS上升沿延迟数据建立时间之后采样。

不同PSRAM芯片时序基本一致,了解一个即可。

-

DRAM

DRAM+关注

关注

40文章

2282浏览量

182978 -

存储单元

存储单元+关注

关注

1文章

62浏览量

16115 -

sram

sram+关注

关注

6文章

757浏览量

114450 -

晶体管

晶体管+关注

关注

77文章

9502浏览量

136947 -

PSRAM

PSRAM+关注

关注

0文章

34浏览量

13260

发布评论请先 登录

相关推荐

(分享)实例解读51单片机完全学习与应用—杨欣ppt

实例解读51单片机完全学习与应用

实例解读51单片机完全学习与应用 PPT课件共16章

PSRAM是指什么?PSRAM接口都有哪些应用呢

PSRAM伪静态随机存取内存

PSRAM,什么是PSRAM

PSRAM在日常生活中的应用

pSRAM与SRAM相比较,它的优势是什么

实例解读模拟电子技术 完全学习与应用pdf

STM32单片机扩展下的IPUS SQPI PSRAM应用领域

Gowin PSRAM Memory Interface IP用户指南

Gowin Video Frame Buffer with PSRAM IP用户指南

EVAL PSRAM GW1NR4用户手册

ESP PSRAM64/ESP PSRAM64H技术规格书

PSRAM完全解读

PSRAM完全解读

评论