一种分选和测试一体的芯片FT测试系统和方法与流程

一种分选和测试一体的芯片ft测试系统和方法

技术领域

1.本发明涉及芯片ft测试技术领域,具体涉及一种分选和测试一体的芯片ft测试系统及方法。

背景技术:

2.随着半导体行业的快速发展,现代ic芯片趋向高集成化和微型化,且设计、生产和制造日益繁杂,任何环节的失误都容易导致产品的失效。ic芯片在完成加工制造工序后,为验证ic功能的正常与完整性,需要进行测试和分选,剔除掉不良品以降低后序成本的损失。采用好的芯片测试方法及测试系统是提高芯片质量水平的关键之一。

3.目前的芯片ft测编流程,需要先对芯片进行电功能测试,然后对电功能测试合格的芯片进行编带和包装,在这两个步骤之间,对于芯片的存储和运输,通常会有较大的时间、空间以及人工成本的浪费,并且存在一定的静电风险。

技术实现要素:

4.针对现有技术存在的问题,本发明的目的在于提供一种分选和测试一体的芯片ft测试系统及方法,其能够直观地对芯片的电功能进行测试,并进行筛选及分类,有效降低芯片测编成本,并规避不必要的静电风险。

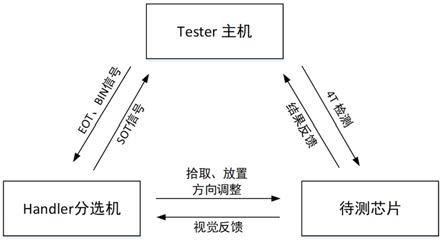

5.为实现上述目的,本发明采用的技术方案是:一种分选和测试一体的芯片ft测试系统,其包括测试主机、分选机以及待测芯片;所述测试主机内部集成有多个adc测试端口;所述分选机具有对待测芯片进行拾取和放置的基本功能;所述待测芯片具有对应的测试端口;所述测试主机和分选机之间以ttl电平信号的方式传输信号;所述待测芯片通过视觉传感器向分选机提供视觉方向信号;所述分选机对待测芯片进行抓取、放置和方向调整动作;所述测试主机对待测芯片进行检测,待测芯片将检测结果反馈给测试主机进行处理。

6.所述ttl电平标准为:输出l:《0.8v,h:》2.4v;输入l:《1.2v,h:》2.0v。

7.所述ttl信号线包括sot、eot、bin三种,其中,sot是指分选机向测试主机发送的测试开始信号;eot是指测试主机测试完成后向分选机发送的测试结束信号;bin是指测试主机向分选机反馈的测试分类信号。

8.所述测试主机对待测芯片进行的检测方式为开尔文测试法。

9.一种分选和测试一体的芯片ft测试方法,其采用上所述的测试系统实现,所述方法包括以下步骤:s1、所述测试主机和分选机进行初始化;s2、分选机拾取待测芯片并对芯片方向进行检测;

s3、分选机将待测芯片放入测试板;s4、分选机发送sot信号给测试主机;s5、测试主机对待测芯片进行电参数测试;s6、测试主机测试完成后发送eot信号给分选机;s7、测试主机发送bin信号给分选机;如果测试芯片为良品,则分选机将芯片送入下一个处理步骤;如果测试芯片为不良品,则分选机将测试芯片送入对应的不良品bin;s8、分选机对测试芯片进行编带或分bin处理;如果测试芯片为良品,分选机会根据编带需要将良品芯片送入编带或送入溢料bin;如果测试芯片为不良品,分选机会将不良品芯片送入所对应的不良品bin。

10.所述步骤s1具体如下:测试主机和分选机的初始化包括:测试主机内部测试端口的自检、内部继电器电平归位和相应电源端口的开启;分选机工位的位置对应和物料清空;测试主机和分选机的通信初始化。

11.所述步骤s2具体如下:分选机先后分别利用光检测方向和电检测方向对待测芯片的方向进行检测,通过对芯片平面的旋转将芯片方向旋转到正确方向。

12.采用上述方案后,能够直观地对芯片的电功能进行测试,并进行筛选及分类,有效降低芯片测编成本,并规避不必要的静电风险。而且,本发明能够较为准确且直观地测量出芯片的电性能,集送料、测试、分选和编带一体化的测试流程,能够实现芯片的快速量产化。

附图说明

13.图1是本发明实施例提供的ft测试系统基本结构图;图2是本发明实施例提供的ttl电平数据帧格式图;图3是本发明实施例提供的开尔文测试方法概述图;图4是本发明实施例提供的handler测试分选设备流程。

具体实施方式

14.应该指出,以下详细说明都是示例性的,旨在对本发明提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本发明所属技术领域的普通技术人员通常理解的相同含义。

15.需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本发明的实例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,在本说明书中使用术语“包含”和/或“包括”时,其指明存在特征、步骤、操作、组件和/或它们的组合。

16.如图1所示,本发明揭示了一种分选和测试一体的芯片ft测试系统,其包括测试主机、分选机以及待测芯片。

17.其中,测试主机内部集成有多个adc测试端口。分选机具有对待测芯片进行拾取和放置的基本功能。待测芯片具有对应的测试端口。测试主机、分选机和待测芯片三者构成一

个两两交互的直接或间接的信号或动作反馈系统。其中,测试主机和分选机之间以ttl电平信号的方式传输sot、eot和bin等信号;待测芯片通过视觉传感器向分选机提供视觉方向信号,分选机对待测芯片进行抓取、放置和方向调整等行为动作;测试主机对待测芯片进行检测,待测芯片将检测结果反馈给测试主机进行处理。

18.如图2所示为ttl电平数据帧格式图,ttl电平标准为:输出l:《0.8v,h:》2.4v;输入l:《1.2v,h:》2.0v。其含义为:ttl输出低电平要小于0.8v,高电平要大于2.4v;输入低于1.2v就认为是0,高于2.0v就认为是1。

19.一般情况下,测试主机与分选机之间的接口(interface)采用ttl电平方式,0v代表低电平,+5v代表高电平,这是一种适用于单测试站工作的速度较快的接口,也是一般测试主机的标配接口。

20.ttl电平接口的极性分为正极性(正逻辑)与负极性(负逻辑)两种,正极性表示信号线上出现的电平为高电平时为有效信号,反之,负极性表示信号线上出现的电平为低电平时为有效信号。

21.ttl信号线包括sot、eot、bin三种,其中sot是指分选机向测试主机发送的测试开始信号;eot是指测试主机测试完成后向分选机发送的测试结束信号;bin是指测试主机向分选机反馈的测试分类信号。

22.上述测试主机对待测芯片进行的检测方式为开尔文测试法,开尔文测试法是一种电阻抗或电压测量技术,使用单独的载电流和电压检测,其关键有点是分离的电流施加单元和电压测量单元,消除了布线和接触电阻的阻抗。如图3所示,当需要测量电阻r的时候,通过单独的电流源施加取样电流,再通过另外的电压测量单元进行测量。对于电流源而言,ri电阻和测量电阻r是串联的,是没有影响的,这时候依然可以保证通过测量电阻r的电流为电流源施加的电流。对于电压测量单元,通常输入端都是高阻抗输入,这个时候,流过ri的电流很小,则ri两端的电压差很小,此时测量的电压就近似等于测量电阻r两端的实际电压。

23.如图4为测试分选工作流程图,首先通过光学检测和电检测进行器件的方向检测,然后校正方向以便进入测试工位进行电参数测试,随后分选机依测试结果对器件进行激光打标和印字检查。随后运用高速工业相机、特制光学模组针对定位方向、尺寸测量、外观缺陷等进行2d引脚/3d5s检测。检测完毕后,进行分选、收料或编带。编带前还需再进行器件带内检测,确保分选的芯片符合需求和质量。

24.基于同一发明构思,一种分选和测试一体的芯片ft测试方法,包括以下步骤:s1、所述测试主机和分选机进行初始化;具体地,测试主机和分选机的初始化包括:测试主机内部测试端口的自检、内部继电器电平归位和相应电源端口的开启;分选机工位的位置对应和物料清空;测试主机和分选机的通信初始化。

25.s2、分选机拾取待测芯片并对芯片方向进行检测;具体地,分选机先后分别利用光检测方向和电检测方向对待测芯片的方向进行检测,通过对芯片平面的旋转将芯片方向旋转到正确方向。

26.s3、分选机将待测芯片放入测试板;具体地,在保证芯片方向无误后,分选机会将待测芯片放入特制的芯片测试板的

测试socket上。socket一般由接触探针和底座组成,作为待测芯片与测试板的临时连接媒介。

27.s4、分选机发送sot(start of test)给测试主机;s5、测试主机对待测芯片进行电参数测试;具体地,测试主机对待测芯片所进行的测试方法为开尔文测试法,这种测试方法能够消除线路阻抗对测试结果的影响。

28.s6、测试主机测试完成后发送eot(end of test)信号给分选机;s7、测试主机发送bin信号给分选机;具体地,如果测试芯片为良品,则分选机将芯片送入下一个处理步骤;如果测试芯片为不良品,则分选机将测试芯片送入对应的不良品bin。

29.s8、分选机对测试芯片进行编带或分bin处理;具体地,如果测试芯片为良品,分选机会根据编带需要将良品芯片送入编带或送入溢料bin;如果测试芯片为不良品,分选机会将不良品芯片送入所对应的不良品bin。

30.综上,本发明将测试主机和分选机集成在一起,并以ttl电平通讯信号的方式将两者结合,形成了一个新的负反馈形式的闭环测试系统,从而缩短两道工序间的空间时间距离,从而较好地规避空间和时间的距离所带来的风险和成本。本发明能够较为准确且直观地测量出芯片的电性能,集送料、测试、分选和编带一体化的测试流程,能够实现芯片的快速量产化。

31.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包括在本发明的保护范围内。

- 一种金银花筛检装置的制作方法

- 矿石全粒级预处理工艺及装置的...

- 一种地板线刀具寿命状态在线检...

- 一种农副产品物流管理货物分类...

- 一种选粉机用进料筛选装置的制...

- 一种选取煤矸石中有价矿物的方...

- 用于土石分离技术的无轴筛沙机...

- 一种煤矸石矿物综合分离方法与...

- 一种从煤矸石中分级分离煤炭的...

- 浮游动物分离方法及分离装置与...

- 还没有人留言评论。精彩留言会获得点赞!