数字IC设计流程及方向介绍

作者:葱哥

摘要:本文主要介绍的数字IC设计的各个流程需要做的工作、用到的各种EDA工具,以及不同数字方向的一些书籍推荐。

分享正文---By复旦微电子XMG师兄

这两年IC行业越来越火,作为一个工作大半年的数字IC设计从业者,在这里谈谈数字IC设计的流程,这是初学者的第一课,无论你是前端设计、验证,还是后端,都需要对整体的芯片有一个初步的了解。希望本文可以对你在选择未来从业方向有一定的帮助。

本文主要介绍的数字IC设计的各个流程需要做的工作、用到的各种EDA工具,以及不同数字方向的一些书籍推荐。

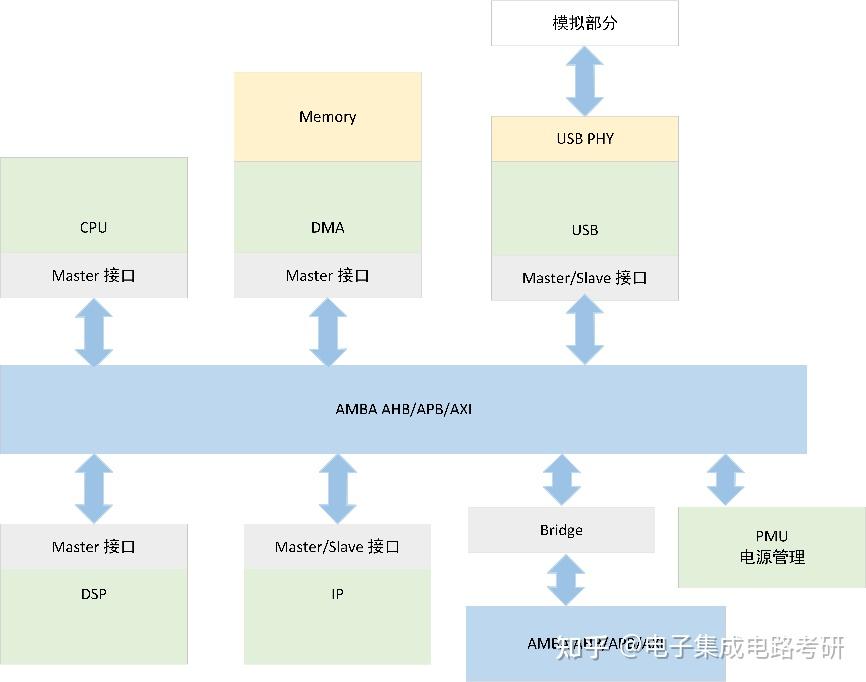

数字芯片中都有什么呢?如下图所示,一款芯片由CPU,memory,DSP通用模块,还有自己设计的例如蓝牙、通信等模块,然后通过总线对这些模块进行集成。

怎么去做一款数字芯片,这里简单介绍一下数字IC的全流程,下图是流程的简单示意图:

1. 芯片架构:做一款芯片之前,公司需要进行调研,比如现在被美国制裁的5G通信芯片,以及比较火的人工智能芯片等等。找到需求之后就可以设计芯片的spec了,先由有经验的数字设计架构师来定架构,规定芯片有哪些功能,用高层次语言(C++、SystemVerilog、Matlab等)设计算法进行模拟仿真,得到一个大致的方案。

推荐的书籍有《计算机体系架构》、《硬件架构的艺术》等。

2. RTL(register transfer level)设计:用Verilog/VHDL/SystemVerilog/Chisel等语言对电路的进行寄存器传输级的设计。设计工程师需要根据架构spec来指定更加详细的设计spec,例如需要定义详细的模块,各个模块的端口信号、模块内各种信号的时序,与模拟的接口等。

使用比较多的编译器有gvim、emacs等。从业者主要分为IP设计和IP集成。设计工程师则是根据需要来设计各种模块,集成工程师则是将设计人员设计的IP以及一些通用IP(例如CPU、总线)连接到一起。

推荐的书籍有《Verilog HDL高级数字设计》、《数字集成电路:电路、系统和设计》、《AMBA总线协议》等。

3. 功能仿真:这部分通常有专业的design verification(DV)工程师来完成。需要搭建验证的环境,目前用的比较多的是UVM,使用SystemVerilog语言。DV工程师需要根据架构spec搭建系统的仿真环境,写各种参考模型,配合设计工程师对功能进行验证。

使用比较多的EDA仿真软件有Candence的NC-Verilog,Synopsys的VCS和Mentor的Modelsim,以及查看波形的Verdi等工具。

推荐的书籍有《SystemVerilog验证》、《芯片验证漫游指南》等。

1. 综合:电路综合是将rtl翻译成满足性能要求的晶体管网表。综合工程师根据芯片制造商提供的基本电路单元库和系统逻辑功能和性能的要求,在众多结构、功能和性能已知的逻辑单元的单元库的支持下,综合工具寻找出一个逻辑网络结构的最佳实现方案,在满足电路功能、速度和面积的条件下,将RTL转换为指定逻辑库中的单元电路的连接。

使用比较多的工具有Synopsys公司的Design Compiler,Cadence公司的RTL Compiler等,需要学习TCL脚本语言。

推荐的书籍有《高级ASIC芯片综合》、各个EDA工具的说明文档等。

2. 静态时序分析:套用特定的时序模型,针对电路分析其是否违反设计者给定的时序限制。它不需要激励向量,可以报出系统中的时序违例,穿插在后端的全部阶段。通过静态时序分析,可以检查设计中的关键路径分布,检查是否有setup/hold违例,检查时钟树的偏移和延时情况等。这些一般由综合工程师来完成。

常用的工具有Synopsys的PrimeTime。

推荐的书籍有《静态时序分析基础及应用》、《Static Timing Analysis For Nanometer Designs》等

3. DFT设计:Design For Test利用实现的辅助性设计,产生高效经济的结构测试向量在ATE上进行芯片测试。主要目的是检查芯片的加工制造过程中产生的缺陷和故障。

DFT工程师主要负责芯片即DFT设计与集成,包括SCAN、MBIST等,负责DFT测试向量大的自动生成与仿真等工作。

推荐的书籍有《DFT数字系统测试和可测性设计》等

4. 形式验证:主要用来检查两个design是否等价。当产生综合的网表之后,需要将RTL与综合Netlist进行对比来确保逻辑上的一致性。同样,在后端完成布局布线之后,也需要将综合网表和PR网表进行等价性检查。

使用的比较多的工具有Synopsys公司的Formality,Cadence公司的Conformal LEC等。这个流程综合工程师(对比RTL和综合网表)和后端工程师(对比综合网表和PR网表)都会使用。

推荐看这些EDA工具的说明文档。

1. 布局布线:Place&Route一般由后端工程师来做。布局就是在版图上给单元、模块分配物理的位置,根据给定的约束进行优化。布线过程用于实现各模块的连接,生成所有连线的几何互联版图,加以适当的约束信息。

常用的工具有Synopsys的IC Compile2,Cadence的Innovus等。

推荐看ICC2/Innovus的说明文档等。

2. 设计规则检查:检查设计规则是否符合芯片制造商的要求,主要是DRC(Design Rule Check)。这个一般由后端工程师来做。

常用的工具有Mentor的Calibre等,推荐看其说明文档。

3. GDSII:当以上所有的流程都已完成之后,就可将GDSII文件交付制造厂商进行生产。整个IC流程是一个不断迭代的过程,每一步如果不能满足要求,都需要重复前面的过程,知道满足要求为止,才能进行下一步。

除了以上介绍到的数字IC设计流程的方向以及推荐的书籍外,作为一个IC初学者,我认为还需要了解一下方面:

1、Linux的使用:基本上各个公司的芯片开发都在Linux系统下,因此也需要了解Linux的基本操作,这里推荐《鸟哥的Linux私房菜》。建议了解基本使用为准

2、脚本语言:脚本在数字IC流程的各个方面都很有用,可以极大减少重复性的工作。推荐学习Shell、Python、Perl等。个人建议学习Python,在工作中还是挺好用的。

3、其他:多了解IC各个方向的发展,保持终生学习的态度。

往期推荐阅读:【下面用超链接】

(1) 模拟IC设计秋招经验分享一

(2) 模拟IC设计秋招经验分享一

(3) 模拟IC设计秋招经验分享一

(4) 模拟IC设计秋招经验分享一

如果有备考微电子专业等择校问题的同学,亦或对微电子感兴趣的同学可以加入下方电子信息和微电子考研交流群:961797189

如果有微电子专业上岸或者在读的同学,将要参加秋招或者春招的同学可以加入下方微电子/集成电路招聘交流群:375117424

文章被以下专栏收录